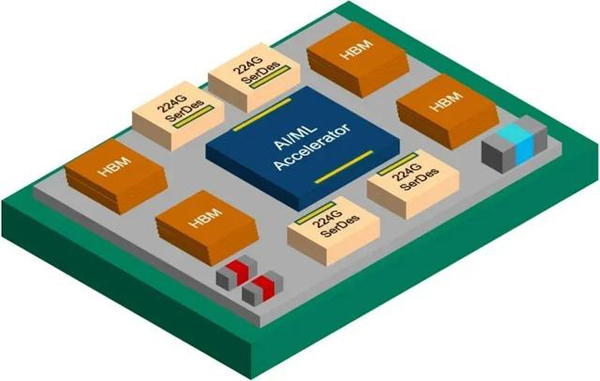

芯片制程获得突破,驱动半导体材料需求升级

随着5G、人工智能、智慧交通等消费电子、汽车电子、计算机等应用领域先进技术的发展,下游应用场景对于芯片性能提出更高的要求,推动芯片制程升级。国内外晶圆厂加紧对于半导体新制程的研发,全球晶圆制造龙头企业台积电、三星等均已向 5nm 以下制程突破;大陆晶圆制造龙头中芯国际也在加紧12nm以下制程工艺的研发。

近年来集成电路制造技术快速发展,新制程带来新的工艺与材料的变化。集成电路制造进入28nm/14nm/7nm制程后,新的晶体管器件、新的工艺和材料不断引入,新的晶体管器件如高K金属栅极(HKMG)晶体管、鳍式场效应晶体管(FinFET),新的工艺如自对准多重成像工艺等,新的材料如钴金属导电层; 同时,先进半导体制程呈现向三维结构转化的趋势。以上集成电路领域的新变化 对晶圆制造主要工艺薄膜沉积工艺——特别是作为这一工艺核心的先进前驱体 材料——提出了更高的要求。

高K金属栅极(HKMG)晶体管是集成电路制程进入 28nm 的 新材料,由于传统二氧化硅栅极晶体管在 28nm 制程后漏电情况大幅增加影响芯片性能,而高 K 金属栅极(HKMG)晶体管则有效解决了这一问题。

双重曝光光刻和鳍式场效应晶体管(FinFET)是集成电路制程进入 14nm 的 新工艺和新器件,其中在双重曝光光刻工艺结合 ArF 浸没式光刻胶可以达到 14nm 以下的集成电路制程;3D 结构的 FinFET 工艺相对于传统的平面晶体管而言减小了晶体管的短沟道效应,同时能够更好地对沟道进行静电控制,FiFET 工艺也需要薄膜沉积工艺及半导体前驱体材料能够填充更小、更高纵深比的沟槽。进入集成电路7nm后,自对准二重/四重曝光成像技术和钴元素等新金属材料制成的薄膜得到应用。

自对准二重/四重曝光成像技术系通过多重曝光实现小尺寸工艺,需要在低温环境下活性好且镀膜均匀的前驱体材料;钴元素则是在新 的技术需求下替代钨元素的新材料,具体表现在含钴的金属前驱体材料等。

此外,更高端的制程工艺需要更加先进薄膜沉积技术(如原子层薄膜沉积 ALD 技术),该技术的先进性以先进ALD前驱体材料作为核心支撑;7nm 以下集成电路制程也需要EUV光刻胶作为必备的生产材料。(来源:思瀚产业研究院 南大光电)

-

麦歌恩-MT6826S高速磁编码器芯片

MT6826S 是麦歌恩微电子推出的新一代基于先进的各向异性 磁阻(AMR)技术的高速高精度角度编码器芯片。该芯片内部集 成了互成45°摆放的两对AMR 惠斯通电桥组成的敏感元件以及 高性能的专用信号处理电路。由于AMR 器件在用作角度测量应 用的时候工作于饱和区(饱和磁场为300高斯),实际工作时,芯 片只对平行于芯片表面的磁场的方向变化做出响应,而与磁场 强度无关。因此MT6826S在使用过程中,对于磁铁本身的加工 误差以及磁铁和芯片的安装距离误差要求相对较低。¥ 0.00立即购买

-

IS09 磁性编码器方案

在工业自动化、机器人技术、伺服驱动等对精度、可靠性和环境适应性要求极高的领域,精准的位置和速度反馈是实现高性能控制的关键。IS09 磁性编码器方案,作为先进的非接触式位置检测解决方案,凭借其独特的技术优势和卓越的工业级表现,正日益成为工程师信赖的核心传感部件。¥ 0.00立即购买

-

MT6501在线编程角度位置磁编码IC

在工业自动化、机器人关节、无人机云台等对角度位置检测要求严苛的应用场景中,MT6501作为一款集高精度、强抗扰性、灵活编程能力于一身的磁旋转编码器芯片,正成为工程师优化系统设计的理想选择。其独特的在线编程(In-System Programming, ISP)功能,彻底改变了传统磁编码器的配置与校准流程,为复杂环境下的位置感知带来前所未有的便捷与精准度¥ 0.00立即购买

-

智能低压水泵无刷电机驱动板方案

高效节能、智能控制的水泵驱动解决方案——智能低压水泵无刷电机驱动板是一款专为低压直流无刷水泵(DC Brushless Pump)设计的高集成度电子驱动控制器。该产品采用先进的无感FOC(磁场定向控制)算法与自适应PID控制技术,支持宽电压输入(12V-48V DC),适用于太阳能水泵、车载水循环系统、农业灌溉、小型工业冷却等场景,具备高效率、低噪声、长寿命和智能化管理等核心优势。¥ 0.00立即购买

-

闭环步进电机驱动板方案

在现代工业自动化、精密仪器和高端装备领域,对运动控制的精度、效率和可靠性要求日益严苛。闭环步进电机驱动板技术应运而生,它融合了传统步进电机的简易性和伺服系统的闭环精度,成为解决步进电机“失步”痛点、提升系统性能的关键技术。以下将从核心原理、系统架构、核心优势、应用场景及选型要素等方面进行层次化阐述。¥ 0.00立即购买

-

云台无刷马达驱动板方案

云台BLDC驱动方案——高精度、低延迟、多场景运动控制核心;高精度云台无刷马达驱动板设计方案:基于FOC控制算法与PID调节的伺服系统优化及运动控制实现¥ 0.00立即购买